- Embedded Solutions

- Systems on Module

- Systems on Chip

- IP Core

- Development Kits

Systems on Chip

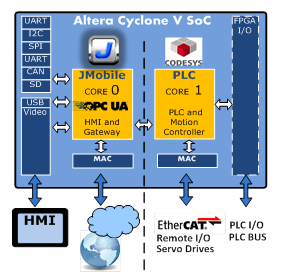

Altera® SoCs integrate an ARM-based hard processor system (HPS) consisting of processor, peripherals, and memory interfaces with the FPGA fabric using a high-bandwidth interconnect backbone. It combines the performance and power savings of hard intellectual property (IP) with the flexibility of programmable logic.

JMSoC is an application suite that provides a complete solution for control connecting equipment and visualizing data.

JMSoC solution allows Altera® CV SoC users to easily develop a customized GUI application using an object-oriented programming in a few weeks without writing a single line of C code.

JMSoC runtime integrate an OPC-UA interface and has been design for systems running Embedded Linux on Altera® CV SoC platform.

JMSoC programming is based on

JMobile Suite (Altera edition) and on CODESYS3.x development workbench for Motion / SoftPLC control applications.